순서논리회로 개요

본 포스팅에서 사용되는 도표는 정보통신기술용어해설에서 차용하였습니다.

정보통신기술용어해설 : http://www.ktword.co.kr/test/view/view.php?no=4078

지난 시간에 우리는 여러 가지의 게이트로 존재하는 조합논리회로를 알아보았다. 불대수의 논리식과 도표로 표현되는 조합논리회로(가산기 디코더 등)을 배우고 이번시간에 같이

공부해볼 내용은 순서 논리회로이다. 순서논리회로를 정확하게 알기 위해서는 펄스의 동작이나 회로도의 표현방식(Active High – Low)등도 알아야하는데, 전자전공이 아닌 필자가 그것을 자신있게 설명하기에는 이치에 맞지 않는 거 같아서 순서논리회로는 시험에 합격할 정도만 바라보고 비교적 가볍게 넘어갈 거 같다.

순서 논리회로는 현재의 상태에 따라 다음의 출력상태가 결정되는 논리회로 이다. 즉 단순한 게이트의 나열이 아니라 ‘현재상태’라는 것이 저장되어있고 그 상태에 따라 출력이 달라지는 회로라는 이야기 이다.

순서 논리 회로는 동기화된 타이밍이 주어지는가 아닌가에 따라서 비동기 순서회로(흔히 래치)와 동기 순서회로(플립플롭)으로 구분된다. 특이한 동작답게 피드백(출력이 입력으로 들어가는 구성)을 가지고 클록 펄스에 의해서 동기화되는 특징을 가진다.

래치(Latch)

래치는 짝수개의 반전소자로 구성된 순서논리회로이다. 래치는 순서신호를 받아들이지 않는 비동기형 순서회로 이며 인버터형 래치, SR래치, D 래치등의 종류를 가진다.

플립플롭(Flip Flop)

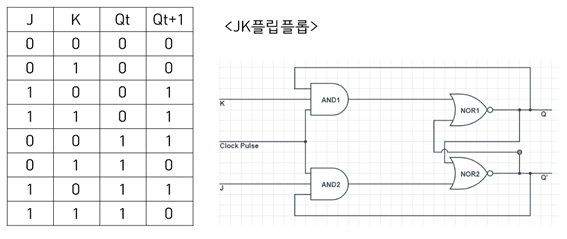

플립플롭은 구성상으로만 보면 래치 순서논리회로에 동기신호인 클럭이 들어가는 형태이다. 1개의 플립플롭은 1비트의 정보를 보관하고 유지하는 순차 회로의 단위로 구분한다. 자주사용되는 JK플립플롭의 형태를 알아보고 나머지는 개념정도만 알아두자.

JK플립플롭은 RS 플립플롭을 개선한 형태로 게이트의 출력을 피드백 받는 구성이다. 이렇게 하여 J와 K입력에(원래 각각 R과 S에 대응) 1이 들어갈 때, 알 수 없던 동작을 토글(반전)으로 개선한 플립플롭이다.

이외에도 플립플롭은 현재상태를 캡처하기 위해 사용되는 지연 플립플롭(D Flip-Flop)과 현재상태를 반전시킬 수 있는 플립플롭(T Flip Flop)이 있다.

정리

이번시간에는상태를 저장하는 회로인 순서논리회로를 알아보았다. 순서논리회로는 동기식 펄스(타이머)가 존재하는지 여부에 따라 래치형(비동기식;단순 피드백)과 플립플롭(동기식)으로 구분되었다. 플립플롭에는 RS(Reset-Set)형과 이를 개선시킨JK형, 딜레이(D), 토글(T)형이 존재하고 래치형은 인버터, SR래치(SR플립플롭에서 신호빠진거), D래치가 존재한다.

다음시간에는

여러 가지 형태의 메모리에 대해서 알아보겠다.

'자격 > 임베디드기사' 카테고리의 다른 글

| [임베디드기사] [필기] 프로그래머블 로직 - HDL (0) | 2023.08.16 |

|---|---|

| [임베디드기사] [필기] 기억소자 - 메모리(Memory) (0) | 2023.08.14 |

| [임베디드기사] [필기] 2진 오류검출과 수정(패리티 비트 / 해밍코드) (0) | 2023.08.14 |

| [임베디드기사] [필기] 논리게이트와 조합논리회로(가산기/복호&부호기/선택&분배기) (0) | 2023.08.14 |

| [임베디드기사] [필기] 수의표현(2진수 / 8진수 / 16진수 / 10진수) (0) | 2023.08.13 |